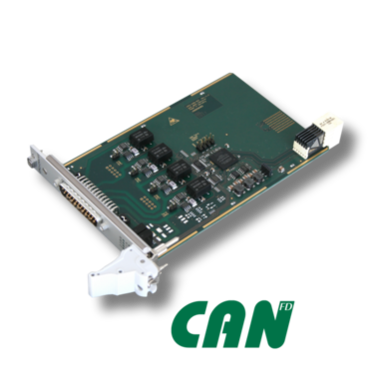

Most CAN controllers available today are connected to the host system via eight or sixteen bit wide buses. Write and especially read accesses to these controllers are very slow compared to the cycle time of modern CPUs. esd electronics has therefore taken it upon itself to solve this problem and the resulting performance problems of the overall system with an FPGA-based CAN controller.

The esdACC is a CAN controller implemented as an IP core in an FPGA. It overcomes the long access times of stand-alone CAN controllers by implementing a 32-bit register interface and streaming data from the CAN bus to the host CPU memory via bus master DMA. Deep FIFO sizes for reading and writing, precise timestamps and the ability to abort a CAN frame even if it is already in the transmit FIFO (as required for more demanding CAN protocols like ARINC825), as well as a register model optimized for the needs of CAN are the features to be highlighted. Depending on the selected features, a large number of CAN controller instances fit into an FPGA and can be addressed by the same host system. Furthermore, the realization in FPGA offers the possibility to integrate sophisticated additional functions or to use the IP core in customer specific assemblies for complex applications.

Error Injection Unit - A Part of the esdACC

For many years, the CAN bus has been used not only in automotive and industrial automation, but increasingly also in safety-critical areas such as medical technology or aerospace. Due to the resulting increase in safety requirements, the need for verification, simulation and testing is also growing.

Due to their principle, the CAN controllers available on the market are not able to send faulty CAN frames or generally violate the CAN standard ISO 11898. The esdACC CAN IP core, supplemented by the Error Injection Unit, is not only able to generate or simulate almost all CAN errors, it can even interactively intervene in the running CAN communication.

The error injection unit has different injection modes, such as CAN arbitration, time triggered or pattern matching, which in combination allow even complex scenarios. With the esdACC Error Injection GUI Tool esd additionally offers a free graphical user interface for the Error Injection Unit.

esdACC solves many Problems

In summary, the esdACC is universally applicable and versatile due to its FPGA-based concept. In the course of the development esd electronics has published technical articles with further information and the advantages of the realized solution. You can download these articles under Further Information in PDF format and convince yourself of the advantages of a product with esdACC for your application.

Further Information

-

esdACC, a Next Generation CAN Controller (EN) Technical article about the CAN Controller from esd (PDF) 247 KB

esdACC, a Next Generation CAN Controller (EN) Technical article about the CAN Controller from esd (PDF) 247 KB -

CAN Send and Receive with Hardware Timestamping (EN) Technical article on Hardware Timestamping by esd (PDF) 56 KB

CAN Send and Receive with Hardware Timestamping (EN) Technical article on Hardware Timestamping by esd (PDF) 56 KB