Die meisten heute verfügbaren CAN-Controller sind über acht oder sechzehn Bit breite Busse mit dem Hostsystem verbunden. Schreib- und insbesondere Lesezugriffe auf diese Controller sind im Vergleich zur Zykluszeit moderner CPUs sehr langsam. esd electronics hat es sich daher zur Aufgabe gemacht, dieses Problem und die daraus resultierenden Performanceprobleme des Gesamtsystems mit einem FPGA-basierten CAN-Controller zu lösen.

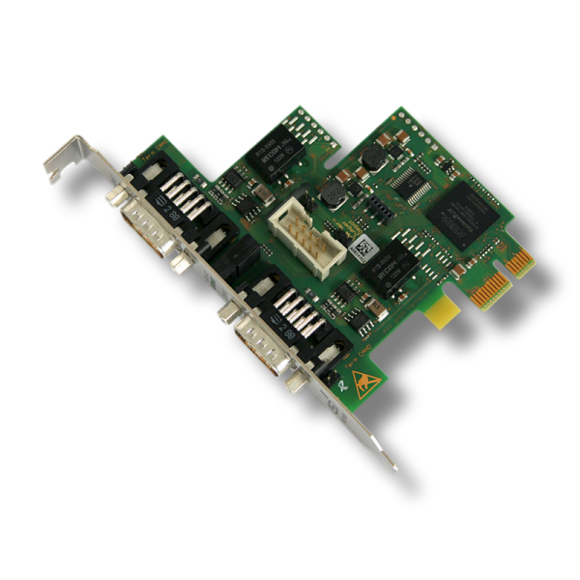

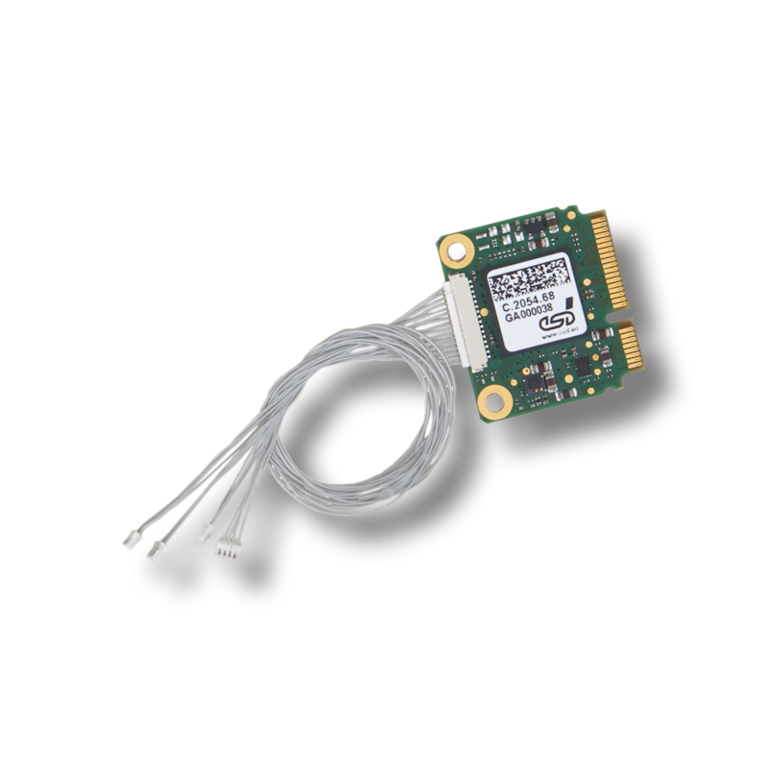

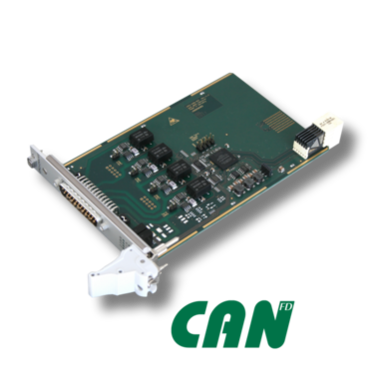

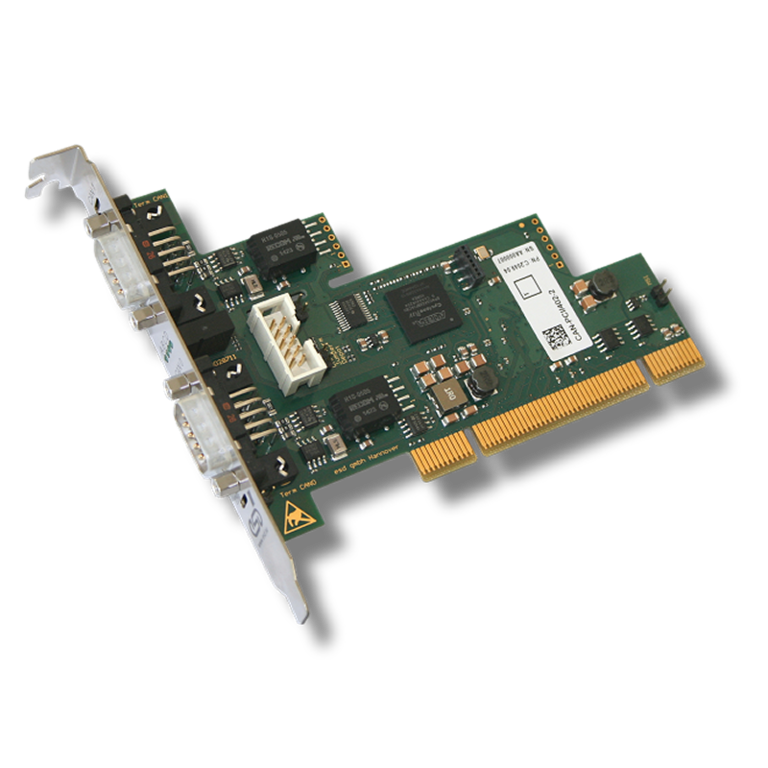

Der esdACC ist ein CAN-Controller, der als IP-Core in einem FPGA realisiert ist. Er überwindet die langen Zugriffszeiten eigenständiger CAN-Controller durch die Implementierung einer 32-Bit-Registerschnittstelle und das Streaming von Daten vom CAN-Bus zum Speicher der Host-CPU über Bus-Master-DMA. Tiefe FIFO-Größen für das Lesen und Schreiben, präzise Zeitstempel und die Fähigkeit, einen CAN-Frame abzubrechen, auch wenn er sich bereits im Sende-FIFO befindet (wie es für anspruchsvollere CAN-Protokolle wie ARINC825 erforderlich ist), sowie ein für die Bedürfnisse von CAN optimiertes Registermodell sind die hervorzuhebenden Merkmale. Abhängig von den gewählten Eigenschaften passen eine Vielzahl von CAN-Controller-Instanzen in ein FPGA und können von demselben Host-System angesprochen werden. Darüber hinaus bietet die Realisierung in FPGA die Möglichkeit, anspruchsvolle Zusatzfunktionen zu integrieren oder den IP-Core in kundenspezifischen Baugruppen für komplexe Anwendungen einzusetzen.

Error Injection Unit - Ein Teil des esdACC

Der CAN-Bus wird seit vielen Jahren nicht nur in der Automobil- und Industrieautomation, sondern zunehmend auch in sicherheitskritischen Bereichen wie der Medizintechnik oder der Luft- und Raumfahrt eingesetzt. Aufgrund der dadurch gestiegenen Sicherheitsanforderungen wächst auch der Bedarf an Verifikation, Simulation und Test.

Die auf dem Markt erhältlichen CAN-Controller sind prinzipbedingt nicht in der Lage, fehlerhafte CAN-Frames zu senden oder generell den CAN-Standard ISO 11898 zu verletzen. Der esdACC CAN IP-Core, ergänzt um die Error Injection Unit, kann nicht nur nahezu alle CAN-Fehler generieren oder simulieren, er kann darüber hinaus sogar interaktiv in die laufende CAN-Kommunikation eingreifen.

Die Fehlerinjektionseinheit verfügt über verschiedene Injektionsmodi, wie z.B. CAN-Arbitrierung, zeitgetriggert oder Pattern-Matching, die in der Kombination auch komplexe Szenarien ermöglichen. Mit dem esdACC Error Injection GUI Tool bietet esd zusätzlich eine kostenlose grafische Benutzeroberfläche für die Error Injection Unit an.

esdACC löst viele Probleme

Zusammenfassend lässt sich sagen, dass der esdACC durch sein FPGA-basiertes Konzept universell einsetzbar und vielseitig verwendbar ist. Im Zuge der Entwicklung hat esd electronics Fachartikel mit weiteren Informationen und den Vorteilen der realisierten Lösung veröffentlicht. Sie können diese Artikel unter weitere Informationen im PDF-Format herunterladen und sich von den Vorteilen eines Produktes mit esdACC für Ihre Anwendung überzeugen.

Weitere Informationen

-

-

CAN Send and Receive with Hardware Timestamping (EN) Fachartikel zum Hardware Timestamping von esd (PDF) 56 KB

CAN Send and Receive with Hardware Timestamping (EN) Fachartikel zum Hardware Timestamping von esd (PDF) 56 KB