High-end CPU for test and application

- NXP® PowerPC® QorIQ® T1022, 1.2 GHz, 64-bit architecture, dual core, double precision floating point unit, Ethernet, ECC RAM

- Xilinx® Artix®-7 FPGA (XC7A75T) for local applications

- RTC

- 2x Gigabit Ethernet, 1x USB 2.0 (host)

- 62 I/Os on PMC-P4 connector, configurable via FPGA as single-ended (LVTTL) or as 31 LVDS pairs

Health features and fallback flash

- Monitoring of local voltages and temperatures

- Fail-safe firmware update by fallback flash

- Watchdog

- Overtemperature protection

Extensive software support

- QNX®, VxWorks® and Linux® BSPs available

- Sample source code for FPGA included in BSP

- Universal bootloader: "Das U-Boot"

- EtherCAT master available

Customized versions available on request

- Processors QorIQ T1014, T1024 or T1042 can be equipped

- Additional connector P6 with (e.g.) 73x LVTTL or 34x LVDS-I/Os

- MRAM (512 KByte)

- Console RS-232 via P4

- CAN (with IRIG-B timestamp) via P4

- Up to 2x 128 MByte Flash

- Up to 2 GByte DDR3 RAM

- Pure PMC version, without P5 and P6 connectors

- BSP for OS-9® on request

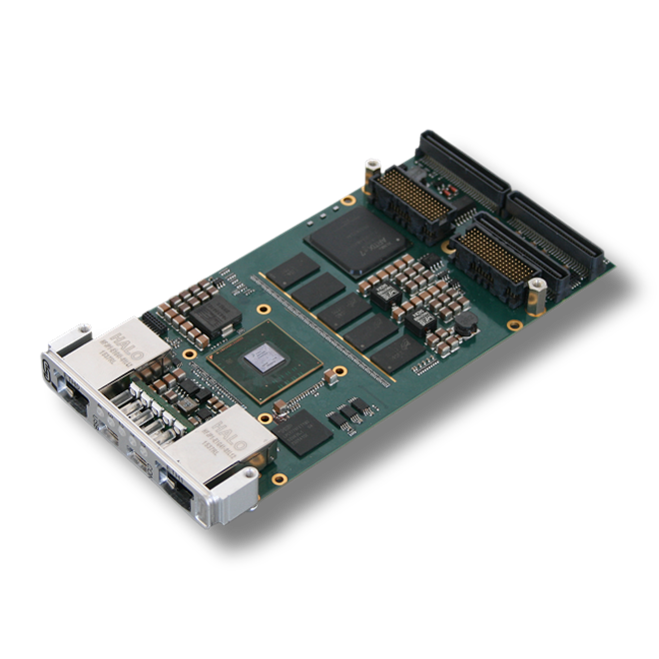

64-Bit XMC PowerPC Host CPU

The XMC CPU/T10 is equipped with one PMC and one XMC interface. The NXP PowerPC QorIQ T1022 with 1.2 GHz supports two 64-bit e5500 Power-Architecture® cores with high-performance Data Path Acceleration Architecture (DPAA) as well as network and peripheral interfaces.

The local 64-bit memory with additional 8 bits ECC has a total capacity of 512 MByte. Non-volatile memory available is 16 MByte SPI flash for the bootloader and 32 KBit I²C EEPROM for the U-Boot environment.

The XMC CPU/T10 is equipped with another 16 MByte backup SPI flash and can be configured for system recovery if a system crash occurred during a firmware update. Alternatively, it can be used for the application software.

FPGA for local applications

The Xilinx Artix-7 FPGA is connected to the CPU for low-latency data exchange via the local bus and for high-bandwidth data exchange via PCI Express®. 62 LVTTL I/Os of the FPGA are routed to the PMC-P4 connector.

XMC/PMC interfaces

The XMC interface with 4-lane PCIe bus is designed according to VITA 42.3™. The PMC interface supports 32-bit/66 MHz PCI bus according to PCI Local Bus Specification 3.0.

Gigabit-Ethernet

Two Gigabit Ethernet interfaces are accessible via the front panel of the XMC-CPU/T10 and provide an excellent basis for EtherCAT® applications.

Software support

The standard boot program "The U-Boot" held in flash memory enables booting of various operating systems from on-board flash as well as via network or USB.

BSPs from esd are available for QNX®, VxWorks® and Linux®. A sample source code for the FPGA is included in the BSPs. The FPGA is programmed using a XILINX toolchain.

The esd EtherCAT master stack is available for all supported operating systems.

Customization on Request

CAN

esd offers standard PIM modules for CAN signals.

Furthermore a CAN IP-core (CAN esdACC) is available on request, implemented in a customized configuration (number of CAN nodes, routing FPGA ↔ P4).

I/Os via P6

Additional 73 LVTTL I/Os at connector P6 or 34 LVDS I/Os are available on request as well as a Serial ATA interface.

CPU Type

Furthermore other CPU-types (T1014, T1042) are applicable, also an additional MRAM and other serial interfaces (RS-232) via P4.

Flash

Up to 2x 128 MByte Flash is available on request.

RAM

Up to 2 GByte DDR3 RAM is available.

PMC only

The XMC-CPU/T10 can be produced without the connectors P5 and P6 if the space on the carrier is limited.

All these options are available for customized series production in reasonable quantities.

Please contact our sales team for detailed information.

Do you have special requirements regarding the product?

We are happy to provide you with a customer-specific option or adjustment to our products when purchasing appropiate quantities. Please contact our sales team for detailed information.

With the help of the button "Add to watchlist" you can save articles on your watchlist.

Afterwards, you can request your saved watch list as a quotation via a contact form.

Hardware

XMC/PMC CPU with PPC QorIQ T1022 1,2 GHz FPGA, 2x GBit-Ethernet

- EtherCAT Master capable

- Ethernet

- PCIe

- USB

- Digital Output

- Digital Input

- USB Port

- Linux

- QNX6/7

- VxWorks

- ARINC825

- CAN-Layer 2

- CANopen

- EtherCAT

- Ethernet

- J1939