# CAN-USB/400-IRIG-B

# 2x CAN (Layer 2, CANopen®, J1939 or ARINC 825, IRIG-B Input)

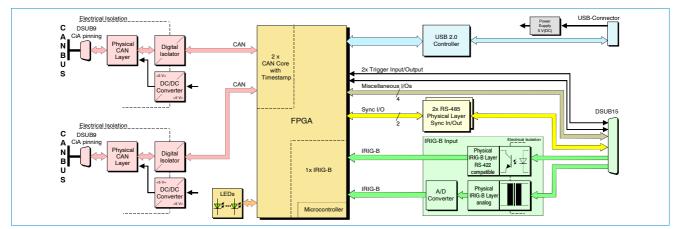

## Two High-Speed CAN Interfaces for USB

- CAN interfaces according to ISO 11898-2 with electrical isolation

- Powered by esd Advanced CAN Core (esdACC) implemented in an FPGA

- Capable of 100% CAN bus load

## Robust and Easy to Handle

- Power supply by USB

- Aluminium case

- Incl. USB cable

- DSUB 15 connector for IRIG-B and other IOs

#### Advanced Diagnostics and Timestamping

- Enhanced diagnostic features

- · Error injection capabilities with ext. trigger

- High resolution hardware timestamping driven by IRIG-B

- CAN interfaces share common time base

#### IRIG-B and Additional Features

- · Analog and digital IRIG-B inputs

- Synchronized timestamps (even without IRIG-B signal) over several CAN-USB/400 via additional RS-485 interface

- External trigger I/Os for Error Injection

- Miscellaneous I/Os for customized functionality

## **Optimized Architecture**

Attached to USB via FIFO's and driven by esd Advanced CAN Core (esdACC), the

CAN-USB/400 is designed for minimum latency CAN communication via USB.

#### **Error Injection**

A feature pretty unique on standard CAN interfaces. Error Injection provides means to simulate error conditions on CAN bus. Bit patterns can be injected into any living CAN bus. Several trigger conditions and modes are provided.

#### Software Support<sup>1</sup>

Operating system independent CAN layer 2 API (NTCAN)

- Driver Support for Windows

- Multiple Higher Level Protocols available for Windows

- CANopen Master- and Slave-Stack

- J1939

- ARINC825

- Drivers and software support for other operating systems are available on request.

#### Technical Specifications:

| reclinical opecinications.        |                                                                                                        |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|

| USB Interface and Microprocessor: |                                                                                                        |

| USB                               | USB 2.0, high-speed 480 Mbit/s                                                                         |

| Memory                            | BlockRAM: 72 KB                                                                                        |

| CAN:                              |                                                                                                        |

| Interface                         | 2x high-speed CAN interface acc. to ISO11898-2, bit rate 1 Mbit/s, differential, electrically isolated |

| CAN controller                    | esdACC in FPGA, acc. to ISO 11898-1                                                                    |

| IRIG-B and I/Os:                  |                                                                                                        |

| IRIG-B interface                  | 1x analog and 1x digital RS-422 compatible (both electrically isolated)                                |

| Trigger I/Os                      | 2x trigger input/output, 3.3 V LVTLL<br>(for Error Injection)                                          |

| Misc. I/Os                        | 4x digital input/output, 3.3 V LVTLL                                                                   |

| General:                          |                                                                                                        |

| Ambient temp.                     | 0+50 °C                                                                                                |

| Humidity                          | Max. 90 %, non-condensing                                                                              |

| Supply voltage                    | Via USB: 5 V                                                                                           |

| Dimensions                        | Approximately 86 mm x 19 mm x 86 mm (excl. connector excess length)                                    |

General (continued):

Connectors CAN: 2x DSUB9 (male)

USB: series B type (female)

IRIG-B, Sync, Trigger, Misc. I/O: DSUB15 (female)

Order Information:

Hardware

Order No.

CAN-USB/400 IRIG-B

2x CAN, 1x IRIG-B, Trigger I/Os, Misc. I/Os

C.2069.06

CAN layer 2 drivers for Windows are included in delivery.

Software Support

CANopen object licences including CD-ROM¹:

CANopen-LCD Windows

C.1101.06

J1939 stack for Windows including CD-ROM¹:

J1939-LCD Windows

C.1130.10

ARINC 825 object licences including CD-ROM¹:

ARINC825-LCD Windows

C.1140.06

ARINC825-LCD Windows

1 For detailed information about the driver availability for your operating system please contact our sales team.

Phone: +49 (0) 511 3 72 98-0 Fax: +49 (0) 511 3 72 98-68 E-mail: info@esd.eu

# CAN-USB/400-IRIG-B

# Driven by esdACC (Advanced CAN Core)

# **5**

#### Basic Product Features:

- CAN ISO 11898-1 protocol compatibility

- 11-bit and 29-bit CAN IDs

- Bit rates from 10 kbit/s up to 1 Mbit/s supported

- Receive buffer (64 CAN messages)

- · Complete access to CAN error counters

- Programmable error warning limit

- Error code capture register

- · Error interrupt for each CAN bus error

- Arbitration lost interrupt with detailed bit position

- Single-shot transmission (no re-transmission)

- Listen only mode (no acknowledge, no active error flags)

- Automatic bit rate detection (software supported bit rate detection)

- Acceptance filter (4-byte code, 4-byte mask)

- Self reception mode (reception of 'own' messages)

- · Busload measurement

## Superior esdACC Features:

- Operating system independently programmable via esd's NTCAN-API

- 32-bit register interface optimized for CAN needs

- · Easy to program

- Transmission and reception of CAN frames with a minimum of register accesses

- RX and TX timestamping (64-bit wide, bit accurate, resolution may vary with input clock, in any case ≤ 62.5 ns, usually 12.5 ns)

- On hardware with IRIG-B interfaces IRIG-B time is used for timestamping

- TX FIFO (16 CAN frames deep)

- Providing the means to generate 100% busload even with non-realtime operating systems

- Providing the means for real back-to-back transmission

- Timestamped Tx FIFO (16 CAN frames deep)

- High priority

- 64 bit timestamp

- Bit time accuracy for CAN transmission

- Frame accurate abortion of transmissions with minimum delay

- e.g. for driver timeouts

- ISO11898-1 conform

- Aborted frames in FIFO won't be blocked by low priority TX

- Hardware timer to provide accurate software timeouts beyond operating system accuracy

## Superior esdACC Features (continued):

- Bus mastering in RX direction takes the load off host CPU (needs bus master capable local bus to host interface)

- Optional integration with 32-bit microcontroller to further relieve host CPU

- Optional different sources for timestamps (e.g. IRIG-B)

- CAN error injection units

- Simulating a wide range of error situations on CAN bus, e.g.:

- ID pollution (100% bus load on certain CAN ID/priority)

- Defective sensor (Destroying all CAN messages of a given CAN ID)

- Different trigger modes

- Bit pattern match

- Time triggered

- Immediate regarding CAN arbitration

- External

- 'Cross CAN bus triggering'

(event on one CAN bus triggers event on another bus)

- Using FPGA technology provides the option to tailor any feature to any customer's needs, including optional integration with customer's FPGA content

- The esdACC IP core has been verified on Xilinx Spartan and Altera Cyclone FPGAs.

For further information on the esdACC IP Core please contact our sales team.