For many years, the CAN bus has been used not only in automotive and industrial automation, but increasingly also in safety-critical areas such as medical technology or aerospace. Due to the resulting increase in safety requirements, the need for verification, simulation and testing is also growing.

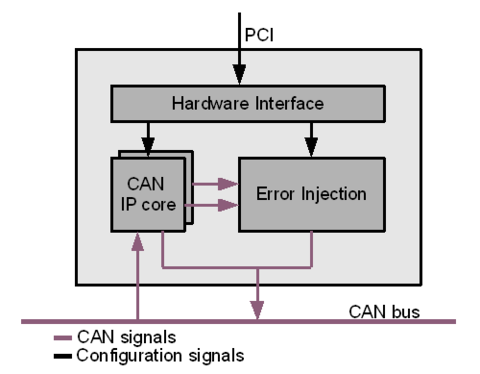

Due to their principle, the CAN controllers available on the market are not able to send faulty CAN frames or to violate the CAN standard ISO 11898 in general. The esdACC CAN IP-Core, supplemented by the Error Injection Unit, can not only generate or simulate almost all CAN errors, it can also even interactively intervene in the ongoing CAN communication.

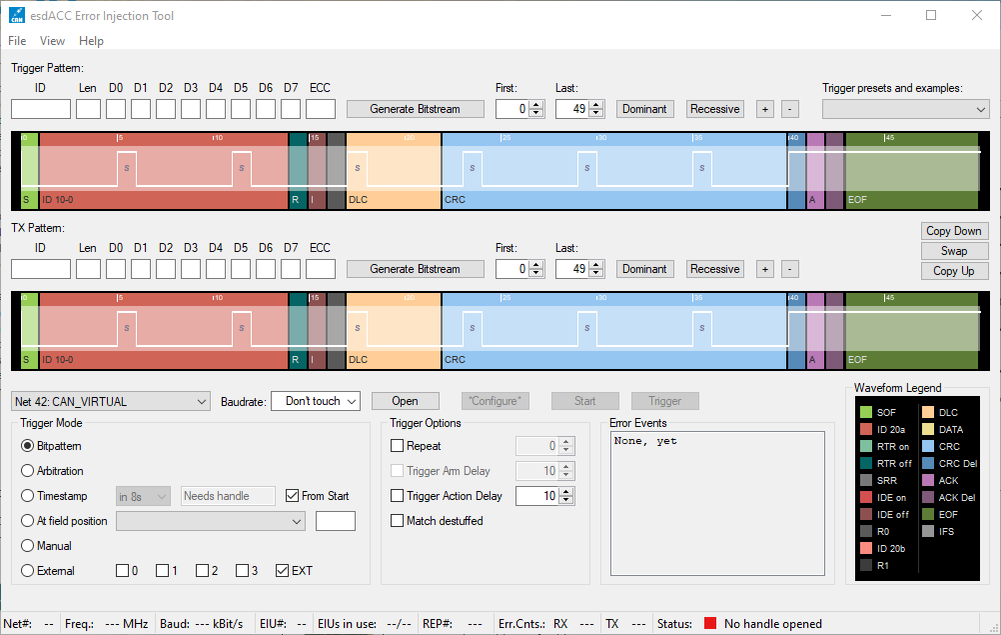

The error injection unit has different injection modes, such as CAN arbitration, time triggered or pattern matching, which in combination allow even complex scenarios. With the esdACC Error Injection GUI Tool esd additionally offers a free graphical user interface for the Error Injection Unit.

esdACC Error Injection GUI-Tool

The esdACC Error Injection GUI tool provides a free graphical user interface for the Error Injection Unit. In addition to the GUI tool, the Error Injection can also be configured and used directly via API calls using the NTCAN API. In this way, automated test cases can be implemented in complex test scenarios. The complete description can be found in chapter 3.13 of the NTCAN Application Developers Manual Part 1. This and the manual for the GUI tool are linked in the further information.

Further Information

-

CAN Error Injection, a Simple but Versatile Approach Technical article from esd about CAN Error Injection as PDF 408 KB

-